2_DVD_ASIC_Design_FLow.pdf

- 1. 11/22/2023 ASIC Design Flow 1 ASIC Design Flow Prof Usha Mehta Professor and PG Coordinator (VLSI Design) Institute of Technology, Nirma University, Ahmedabad usha.mehta@nirmauni.ac.in

- 2. 11/22/2023 ASIC Design Flow 2 Acknowledgement…. • This presentation has been summarized from various books, papers, websites and presentations related to the topic all over the world. I couldn’t remember where these large pull of hints and work come from. However, I’d like to thank all professors and scientists who created such a good work on this emerging field. Without those efforts in this very emerging technology, these notes and slides can’t be finished.

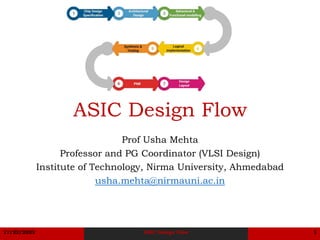

- 3. 11/22/2023 ASIC Design Flow 3 Basic ASIC Design Flow

- 4. 11/22/2023 ASIC Design Flow 4

- 5. 11/22/2023 ASIC Design Flow 5 • The above basic design flow is somehow over simplified in the sense that it only connects the design tasks in one direction. • Interactions between different stages, especially the influences of later stages on earlier ones, are not shown. • In reality, a design cannot be done in such a singular path. – If the timing analysis finds that the delay of the critical path is longer than that required by a clock period, we have to go back to the physical design to modify the layout. – If the problem cannot be resolved inside the physical design stage we then have to go back further to the circuit design to add buffers. – If we cannot resolve the problem through the modification of physical or circuit design, we would have to go back another stage to change the architecture design.

- 6. 11/22/2023 ASIC Design Flow 6 • Most interference between different design stages is actually due to system performance requirements and variable remitting solutions at different stages. – As a consequence, we need to have loops in the design flow. • In general we want to go backward as little as possible. – A subsequent problem is that we might be end up cycling through these stages endlessly. – This issue is called timing closure

- 7. 11/22/2023 ASIC Design Flow 7 Timing Closure

- 8. 11/22/2023 ASIC Design Flow 8 Verification and Testing

- 9. 11/22/2023 ASIC Design Flow 9 System Specification • A real ASIC design practice starts from understanding the application and writing a clear and complete specification in terms of VLSI terminology, such as input/output signals, clock rate, protocol definition, operation mode and etc. • Writing a specification for an ASIC project includes – Understanding the application – Communicating with customer for whom ASIC chip is designed – Converting application terminology into circuit design terminology – Defining system settings – Listing the performance criteria, and – Selecting the process

- 10. 11/22/2023 ASIC Design Flow 10 Architectural Design • Architecture design • Architecture probably plays the most important role in determining the quality of a designed chip. • Experience in IC design and insight into the application contribute to the architecture choice. • Currently, architecture design still depends on the wisdom of the designer instead of on CAD tools, since there are too many factors involved. • Unfortunately the influence of different factors usually conflicts with each other. • Decisions on the architecture, e.g., RISC/CISC, # of ALU’s, pipeline structure, cache size, etc. Such decisions can provide an accurate estimation of the system performance, die size, power consumption, etc.

- 11. 11/22/2023 ASIC Design Flow 11 Functional/Behavioural Design • Identify main functional units and their interconnections. No details of implementation. • Functional design is generally done with HDL

- 12. 11/22/2023 ASIC Design Flow 12 Register Transfer Level + + 0010 0001 0100 0011 • Components, data types • Design the logic, e.g., Boolean expressions, control flow, word width, register allocation, etc. • RTL is expressed in a HDL mostly synthesized from behavioral description

- 13. 11/22/2023 ASIC Design Flow 13 Logic Level • Discrete Level, Discrete Time • Design the circuit including gates, transistors, interconnections, etc. The outcome is called a netlist. • Homework ISCAS Gate level Netlist

- 14. 11/22/2023 ASIC Design Flow 14 Circuit level • Continuous Voltage, Continuous time

- 15. 11/22/2023 ASIC Design Flow 15 Layout • Convert the netlist into a geometric representation. The outcome is called a layout.

- 16. 11/22/2023 ASIC Design Flow 16 Few more words… • Circuit Partitioning – Partition a large circuit into sub- circuits (called blocks). Factors like #blocks, block sizes, interconnection between blocks, etc., are considered. • Floorplanning – Set up a plan for a good layout. Place the modules (modules can be blocks, functional units, etc.) at an early stage when details like shape, area, I/O pin positions of the modules, …, are not yet fixed. • Placement – Exact placement of the modules (modules can be gates, standard cells, etc.) when details of the module design are known. The goal is to minimize the delay, total area and interconnect cost.

- 17. 11/22/2023 ASIC Design Flow 17 • Routing – Complete the interconnections between modules. Factors like critical path, clock skew, wire spacing, etc., are considered. Include global routing and detailed routing. • Compaction – Compress the layout from all directions to minimize the total chip area. • Verification – Check the correctness of the layout. Include DRC (Design Rule Checking), circuit extraction (generate a circuit from the layout to compare with the original netlist), performance verification (extract geometric information to compute resistance, capacitance, delay, etc.)

- 18. 11/22/2023 ASIC Design Flow 18 Cont…. • Logic Synthesizer • Translation from RTL specification to netlist • Adequate for the design that do not have critical performance parameter • Provides room to make design improvement • Understanding of device architecture is necessary • Gate Level Simulation • To ensure correctness of synthesis translation • Vendor supplied parameters are used to simulate the actual target device parameters

- 19. 11/22/2023 ASIC Design Flow 19 Cont… • Extraction • Actual resistance and capacitance figures modelled for interconnections are extracted to simulate timing performance • Post Layout Simulation • Functionality taking care of timings • Time extraction imported • Both gate and interconnection delays are considered • Back Annotation • To update the initial circuit data with information that was obtained later in the design cycle • Passing the information related to the extra load that may occur in practice

- 20. 11/22/2023 ASIC Design Flow 20 Cont… • Extended Testing • For ASIC, GA, SoG. • Not for FPGA • Device Programming • Via JTAG port • For FPGA

- 21. 11/22/2023 ASIC Design Flow 21 VLSI Design Tools • By Chip vendor • By third party • Cadence • Mentor Graphics • Synopsis • Microwind

- 22. 11/22/2023 ASIC Design Flow 22

- 23. 11/22/2023 ASIC Design Flow 23 Coverage of my area…. • ASIC • Full Custom • CMOS Design • Simulation • Layout • SemiCustom • Verification • Gate Array • Std. Cell • DFT • STA • FP-Floor Plan • CTC – Clock Tree Synthesis • FPGA • HDL Entry • Place and Route

- 24. 11/22/2023 ASIC Design Flow 24 Thank you!